澳门新浦京游戏下载 英特尔 Nova Lake 搞定器尺寸曝光:单芯单方面积远超 AMD,吸收台积电代工

发布日期:2026-02-19 13:42 点击次数:197

IT之家 2 月 11 日音讯,英特尔下一代 Nova Lake 搞定器更多细节逐步流出。

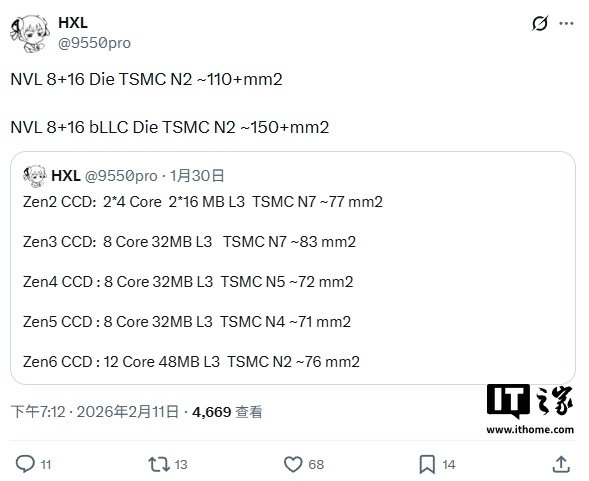

字据爆料者 HXL 本日最新露馅的信息,Nova Lake 吸收台积电 N2 工艺,计较芯片(Compute Tile)吸收 8 个 P 核 +16 个 E 核的基础确立,其裸晶圆面积(Die Size)远超 AMD 竞品。

行动参考,AMD 现存 Zen 5 搞定器的 CCD 为 8 核,晶圆面积约 71mm²;而 Zen 6 瞻望将把每个 CCD 栽植至最多 12 核,面积算计约 76mm²。

按此对比,Nova Lake 表率芯单方面积比 Zen 5 CCD 大了约 55%,比拟 Zen 6 CCD 大了约 44%。

Nova Lake 桌面搞定器与转移搞定器均吸收 8P+16E 基础确立,但也领略过屏蔽部分中枢提供面向初学与主流阛阓的 4P+8E 型号。

天然英特尔也曾推出了基于 Intel 18A 制程的 Panther Lake 搞定器,但由于性能库的原因无法提供桌面搞定器版块,而下一代 Nova Lake 的计较芯片将和解吸收台积电 N2 工艺。

在中枢与结构方面,现存爆料表露 Nova Lake 将搭载基于 Coyote Cove 架构的 P 核,澳门新浦京游戏app以及基于 Arctic Wolf 架构的 E 核。P 核部分的布局则是每簇 2 个中枢,并为每个簇确立 4MB 的 L2 缓存。

肖似于 Panther Lake,英特尔还会在孤苦区域内置 4 个 LPE 低功耗中枢(这部分中枢无法超频),但可用于低功耗运转场景,以至不错在 P 核与 E 核被禁用的情况下单独职责。

另外,爆料表露英特尔 Nova Lake 还将推出双计较芯片的 52 核旗舰型号。表率双芯片版块的面积约为 220mm²;而吸收 bLLC 大缓存的双芯片版块接近 300mm²,最大可提供 288MB 的 L3 缓存,总缓存范畴(L2+L3)可达到 320MB,但 TDP 也将提高到 175W。

尽管计较芯片自身占用面积权贵增多,但爆料称这些 sku 仍会吸收消灭封装,何况会使用不异的 LGA1954 插槽。

值得一提的是 bLLC 与 AMD X3D 堆叠时刻并不调换,天然英特尔也有肖似 X3D 的特等缓存时刻,但当今并未在 Nova Lake 上诈欺。

{jz:field.toptypename/}关联阅读: ]article_adlist--> 声明:新浪网独家稿件,未经授权辞让转载。 -->